อินเทลเผยร่วมกระบวนการผลิตชิป Intel 18A ก่อนทาง TSMC N2 ด้วยโรงงานชิป Fab 52 Ramp ของตัวเองอย่างเป็นทางการ

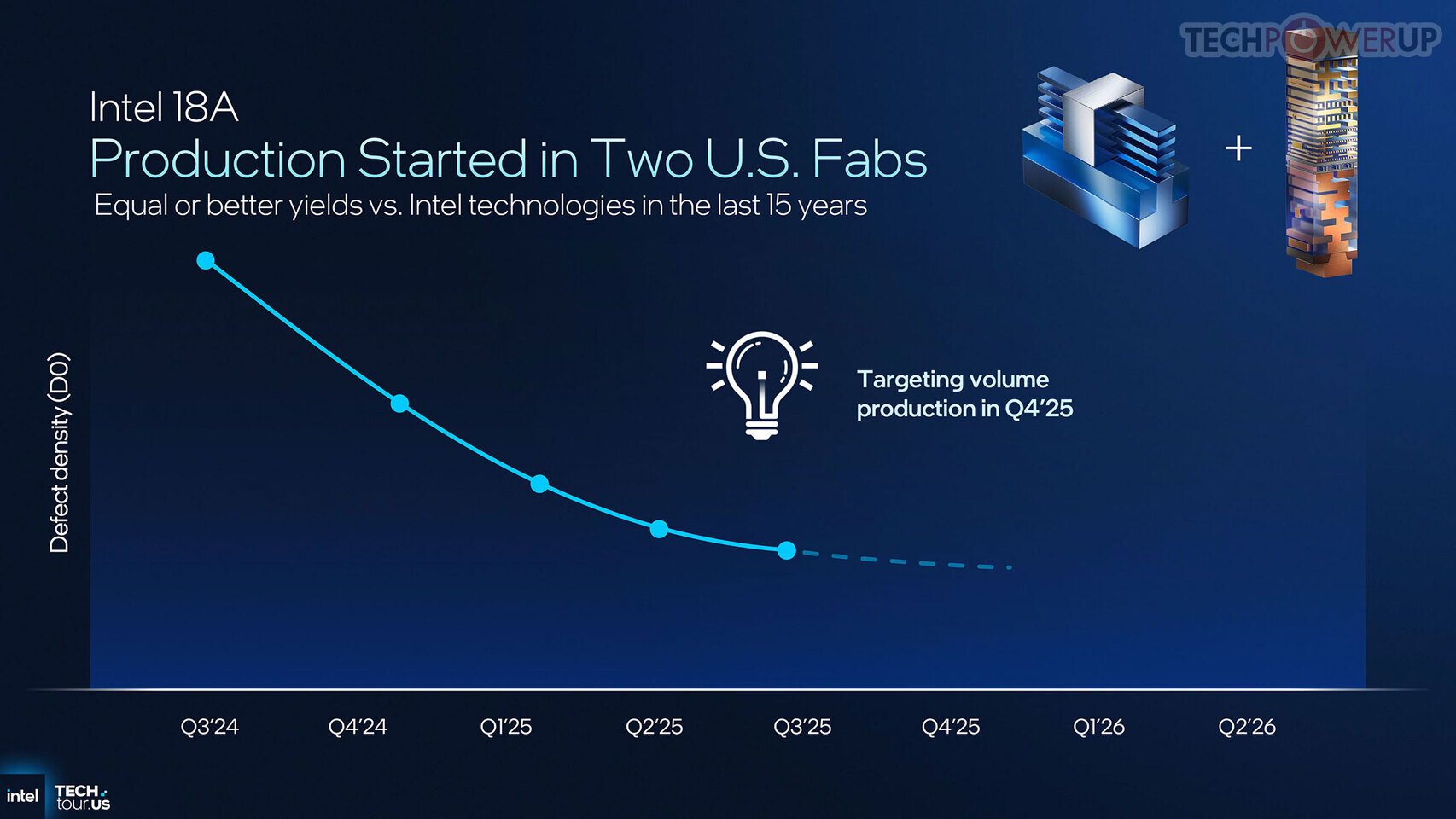

Intel ประกาศในสัปดาห์นี้ว่าโปรเซสเซอร์ Panther Lake ได้เข้าสู่การผลิตจำนวนมากที่ Fab 52 โดยใช้โหนด 18A ของบริษัท ซึ่งได้รับการยกย่องว่าเป็นกระบวนการผลิตขนาด 2 นาโนเมตรรุ่นแรกที่สามารถผลิตได้ในปริมาณมาก ความสำเร็จครั้งนี้ทำให้ Intel มีข้อได้เปรียบเล็กน้อยในด้านเวลาการผลิตเหนือคู่แข่งอย่าง TSMC ที่มีโหนด N2 และ Samsung ที่มีโหนด SF2 อย่างไรก็ตาม การเป็นผู้นำไม่ได้รับประกันความเป็นผู้นำที่ยั่งยืน ลูกค้า พันธมิตร และนักลงทุนจะให้ความสำคัญกับความสามารถของ Intel ในการรักษาผลผลิตแบบพาราเมตริก ควบคุมต้นทุนการผลิตต่อหน่วย และขยาย 18A ให้เกินขีดจำกัดของไทล์การประมวลผล แม้ว่า Intel จะได้แบ่งปันการปรับปรุงในด้านความหนาแน่นของข้อบกพร่องและผลการทดสอบการทำงานเบื้องต้น แต่ตัวชี้วัดผลผลิตแบบพาราเมตริกที่ครอบคลุมซึ่งแสดงให้เห็นถึงการบรรลุเป้าหมายด้านพลังงาน ประสิทธิภาพ และความถี่อย่างต่อเนื่องยังคงไม่ได้รับการเปิดเผย การจัดส่งเบื้องต้นและตัวเลขการผลิตขั้นต้นจะเป็นตัวกำหนดว่าการเริ่มต้นการผลิตครั้งนี้จะเป็นสัญลักษณ์หรือเป็นปัจจัยสำคัญสำหรับการฟื้นตัวของการผลิตของ Intel

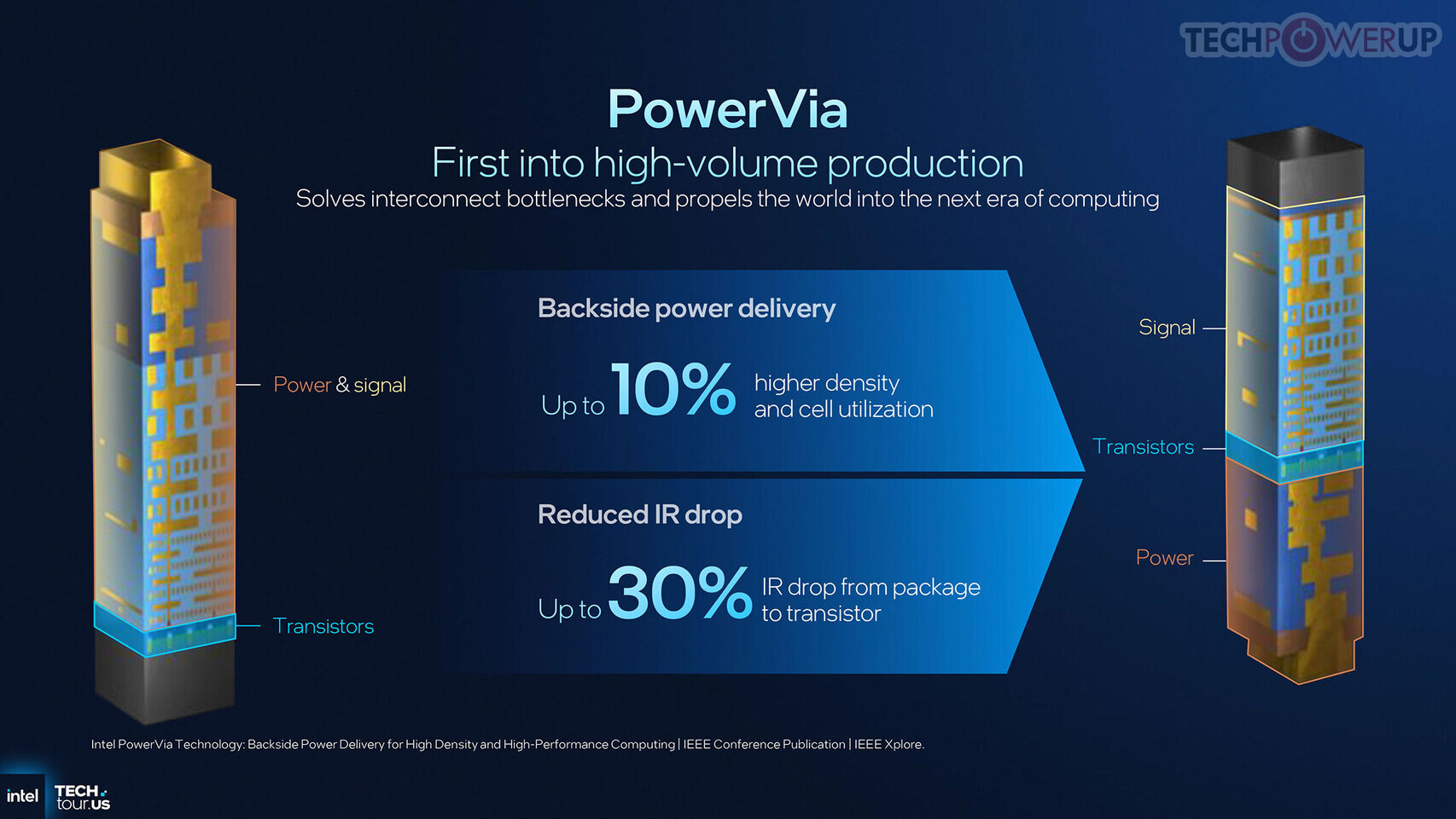

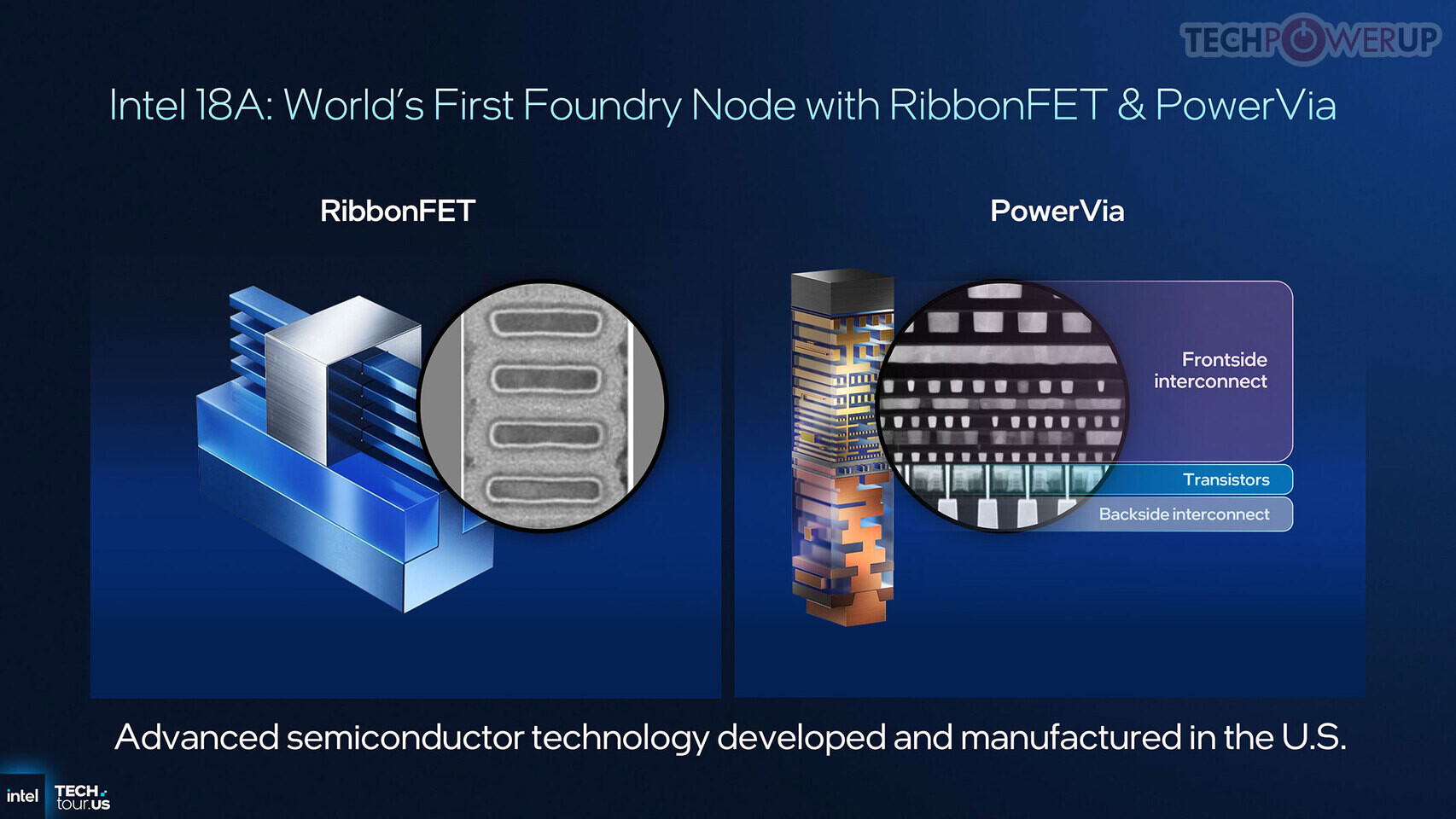

ในระดับทรานซิสเตอร์ โหนด 18A นำเสนอนวัตกรรมสำคัญสองประการ ได้แก่ ทรานซิสเตอร์แบบ RibbonFET ที่ใช้เกตรอบทิศทาง และการจ่ายพลังงานด้านหลัง PowerVia RibbonFET แทนที่ครีบ FinFET แนวตั้งด้วยริบบิ้นซิลิคอนแนวนอนบางๆ ที่หุ้มด้วยวัสดุเกต ซึ่งช่วยเพิ่มประสิทธิภาพการควบคุมไฟฟ้าสถิต ลดการรั่วไหล และทำให้เกตมีความยาวสั้นลง Intel รายงานว่าความยาวเกตสั้นลงประมาณ 5-10% เมื่อเปลี่ยนจาก FinFET มาเป็น RibbonFET บน 18A และอ้างว่าพลังงานต่อทรานซิสเตอร์ลดลงมากกว่า 20% PowerVia ย้ายโครงข่ายไฟฟ้าไปยังด้านหลังของเวเฟอร์ ทำให้โลหะด้านหน้ามีพื้นที่ว่างสำหรับการกำหนดเส้นทางสัญญาณ ลดเส้นทางไฟฟ้า และลดแรงดันไฟฟ้าตกที่อัตราการสลับสูง การเปลี่ยนแปลงเหล่านี้ร่วมกันช่วยลดพลังงานในการสลับและมอบความยืดหยุ่นที่มากขึ้นให้กับนักออกแบบในการเพิ่มความถี่หรือลดการใช้พลังงานในโน้ตบุ๊กและการออกแบบอุปกรณ์พกพาอื่นๆ

ผลกระทบของทรานซิสเตอร์เหล่านี้และการปรับปรุงพลังงานต่อผลิตภัณฑ์สำเร็จรูปขึ้นอยู่กับบรรจุภัณฑ์และการออกแบบระดับไทล์ Panther Lake ใช้ Foveros-S ซึ่งเป็นวิธีการบรรจุภัณฑ์แบบ 2.5D ที่มีการเชื่อมต่อแบบพิทช์ละเอียดประมาณ 36 ไมโครเมตร เพื่อรวมไทล์การประมวลผล กราฟิก และแพลตฟอร์มเข้าไว้ในระบบเดียวบนชิป วิธีการแบบโมดูลาร์นี้ช่วยให้ Intel สามารถผลิตไทล์แต่ละชิ้นบนโหนดกระบวนการให้เหมาะสมกับการใช้งานมากที่สุด ช่วยเพิ่มผลผลิตเชิงฟังก์ชันและลดความเสี่ยงที่เกี่ยวข้องกับไดย์โมโนลิธิกขนาดใหญ่ ใน Panther Lake ไทล์การประมวลผลสร้างขึ้นบน Intel 18A, ไทล์ GPU 12-Xe ผลิตบน TSMC N3E, ไทล์ 4-Xe ขนาดเล็กกว่าสร้างขึ้นบน Intel 3 และตัวควบคุมแพลตฟอร์มทำงานบน TSMC N6 การผสมผสานระหว่างโหนดและไทล์เหล่านี้ทำให้ Intel มีความยืดหยุ่นในการเพิ่มประสิทธิภาพ ประสิทธิภาพ และระยะเวลาในการนำออกสู่ตลาด ในขณะเดียวกันก็อนุญาตให้ทำซ้ำระบบย่อยกราฟิก การประมวลผล และ I/O ได้อย่างอิสระ