ชิปต่ำกว่า 1nm ยังไม่มาเร็วอย่างที่คิด! โรดแมปล่าสุดเผย เทคโนโลยี Sub-1nm อาจต้องรอถึงปี 2034

| Share | Tweet |

ชิปต่ำกว่า 1nm ยังไม่มาเร็วอย่างที่คิด! โรดแมปล่าสุดเผย เทคโนโลยี Sub-1nm อาจต้องรอถึงปี 2034

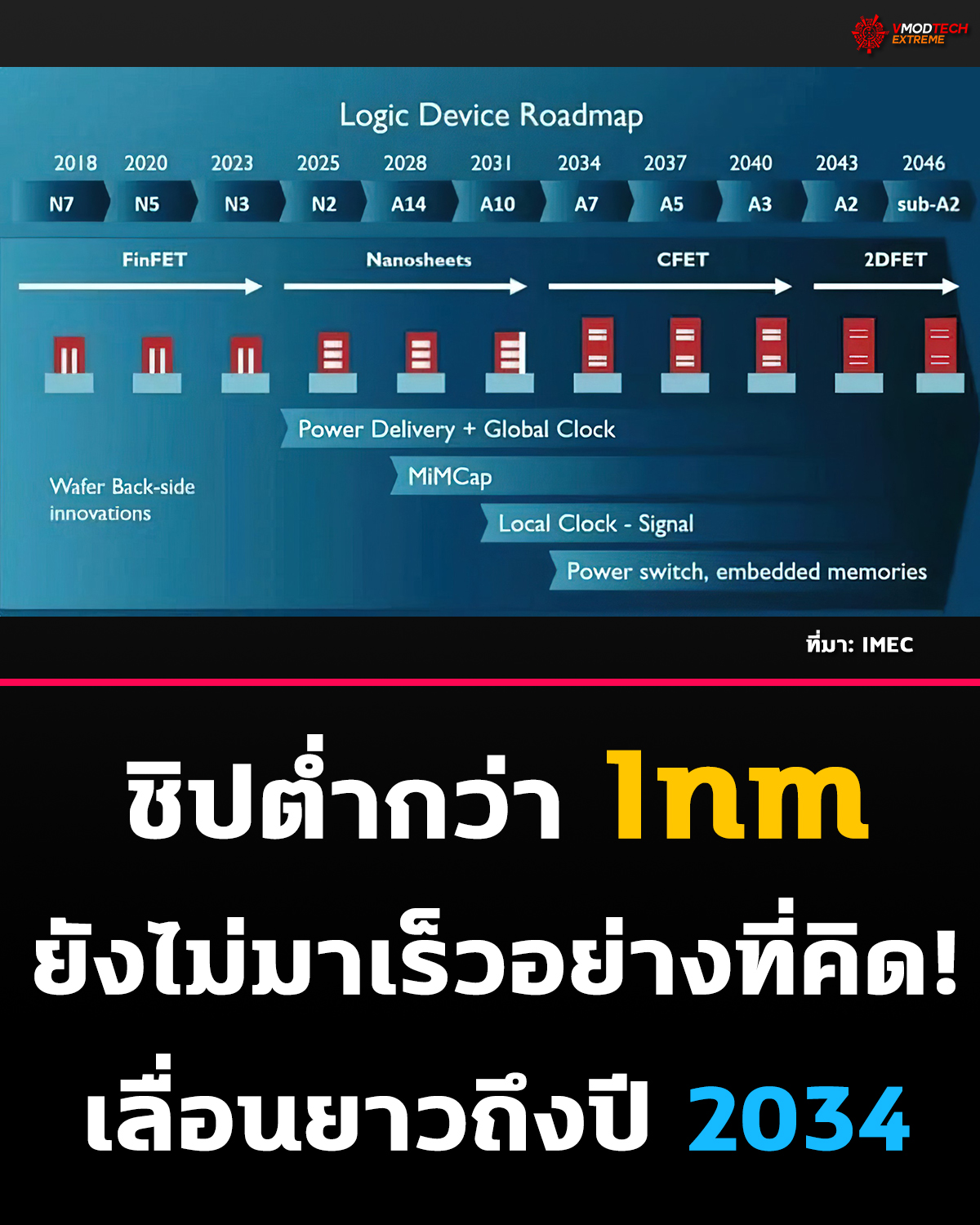

ความก้าวหน้าของเทคโนโลยีชิปกำลังเข้าสู่ช่วง “ชะลอตัวเชิงกายภาพ” อย่างชัดเจน โดยโรดแมปล่าสุดจาก IMEC ระบุว่า กระบวนการผลิตระดับต่ำกว่า 1 นาโนเมตร (Sub-1nm) จะยังไม่เกิดขึ้นจริงจนถึงราวปี 2034

ในช่วงเปลี่ยนผ่าน อุตสาหกรรมจะยังคงใช้เทคโนโลยี Nanosheet หรือ GAA (Gate-All-Around) ต่อไปจนถึงระดับประมาณ 1nm ก่อนจะเข้าสู่ยุคใหม่ของ CFET (Complementary FET) ซึ่งเป็นการซ้อนทรานซิสเตอร์ในแนวตั้ง เพื่อเพิ่มความหนาแน่นและประสิทธิภาพของชิป

โรดแมประบุว่า เทคโนโลยีระดับ 0.7nm (A7) จะเริ่มต้นในปี 2034 ก่อนจะพัฒนาไปสู่ 0.5nm ในปี 2036 และ 0.3nm ภายในปี 2040 ซึ่งสามารถเพิ่มความหนาแน่นของทรานซิสเตอร์ได้สูงถึง 80% เมื่อเทียบกับยุคก่อนหน้า

หลังจากนั้น อุตสาหกรรมจะก้าวเข้าสู่ยุค 2D FET ซึ่งใช้วัสดุใหม่ระดับอะตอม โดยคาดว่าจะเริ่มใช้งานในโหนด 0.2nm (A2) ภายในปี 2043 และพัฒนาไปสู่ระดับต่ำกว่า 0.2nm ในช่วงปี 2046

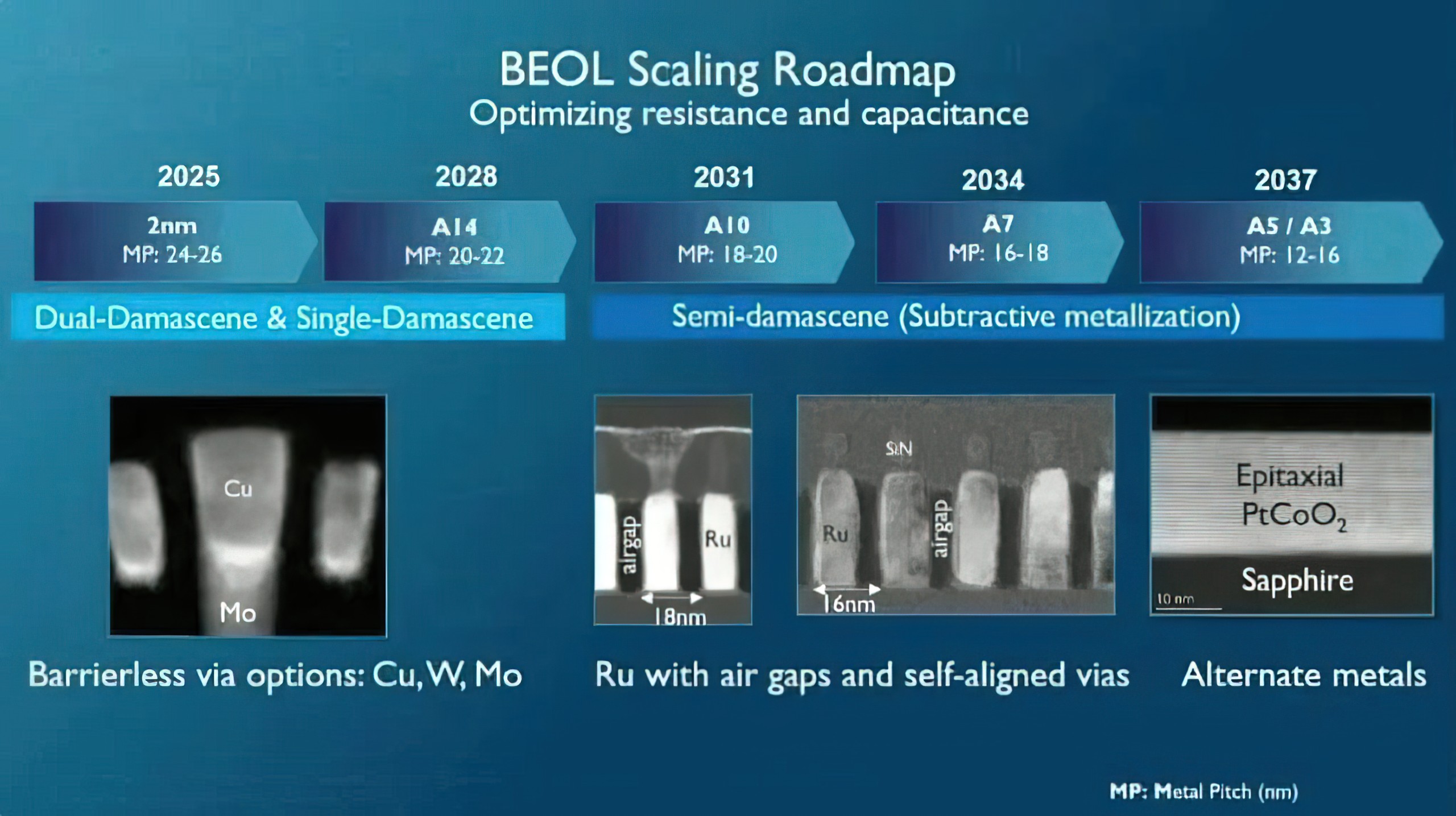

นอกจากการย่อขนาดทรานซิสเตอร์แล้ว การพัฒนาในส่วนของ interconnect และวัสดุใหม่ เช่น Ruthenium (Ru) และ PtCoO₂ ก็มีบทบาทสำคัญในการลดความต้านทานและเพิ่มประสิทธิภาพของชิป

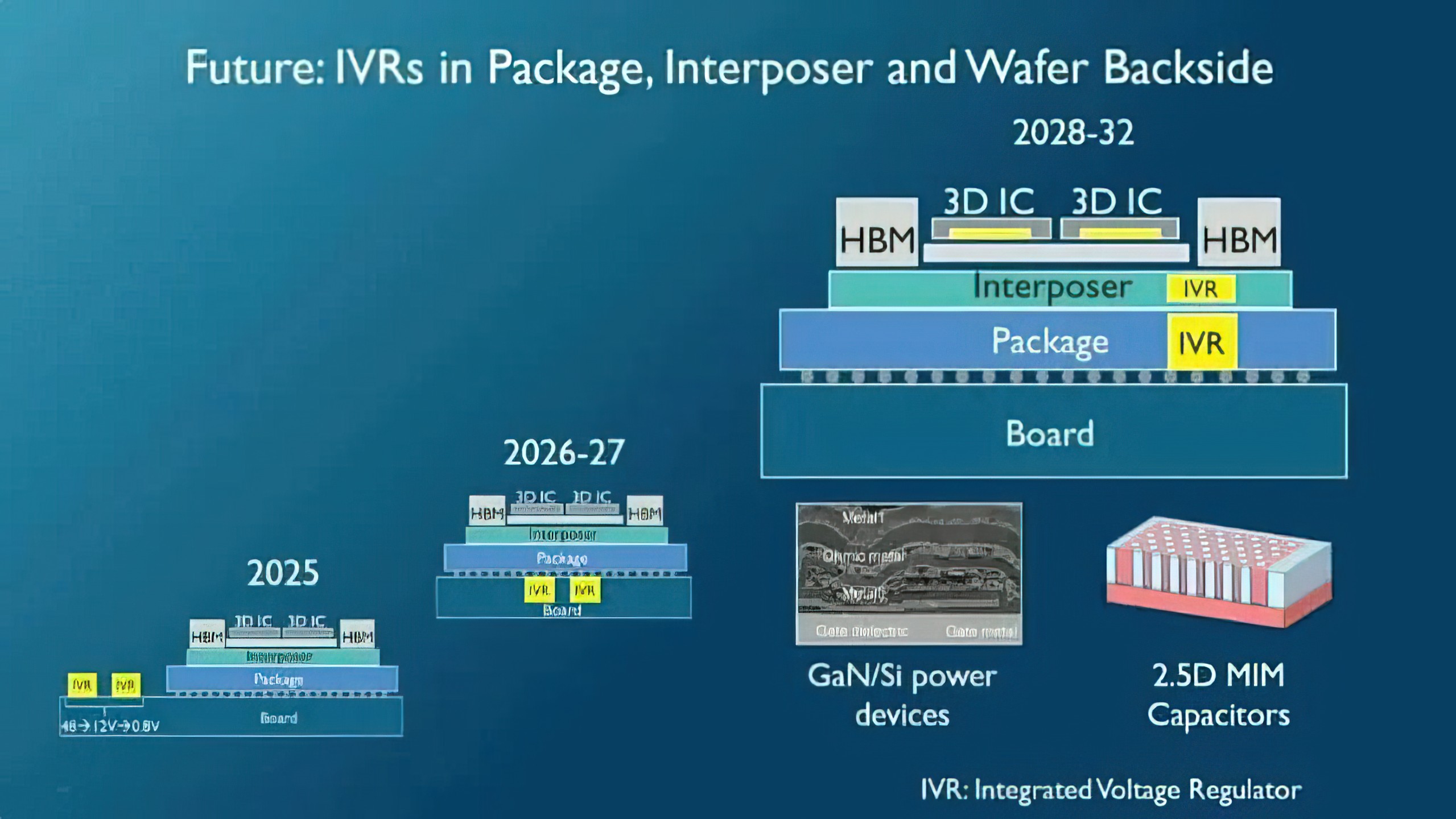

อย่างไรก็ตาม แนวโน้มสำคัญที่เห็นได้ชัดคือ อุตสาหกรรมไม่ได้พึ่งพาการ “ย่อขนาด” เพียงอย่างเดียวอีกต่อไป แต่หันไปใช้เทคโนโลยี 3D stacking, chiplet และ advanced packaging เพื่อเพิ่มประสิทธิภาพโดยรวมของระบบ

ทั้งหมดนี้สะท้อนว่า แม้ Moore’s Law จะช้าลง แต่การพัฒนาในอุตสาหกรรมเซมิคอนดักเตอร์ยังคงเดินหน้าต่อ เพื่อรองรับความต้องการของ AI, HPC และเทคโนโลยีอนาคต

ที่มา: IMEC /

EN

EN